Anda kini mengikuti

Ralat mengikuti pengguna.

Pengguna ini tidak membenarkan pengguna untuk mengikuti mereka.

Anda telah mengikuti pengguna ini.

Pelan keahlian anda hanya membenarkan 0 mengikuti. Naik taraf di sini.

Berjaya menyahikut

Ralat tidak mengikuti pengguna.

Anda berjaya mengesyorkan

Ralat mengesyorkan pengguna.

Sesuatu telah berlaku. Sila segar semula halaman dan cuba lagi.

E-mel berjaya disahkan.

rawalpindi,

pakistan

Sekarang jam 5:05 PTG di sini

Menyertai Oktober 15, 2011

0 Cadangan

Elecguru011

@Elecguru011

0.0

0.0

83%

83%

rawalpindi,

pakistan

N/A

Pekerjaan Disiapkan

N/A

Mengikut Bajet

N/A

Tepat Pada Masa

N/A

Kadar Upah Semula

Embedded Design Enigneer with expertise in FPGA and DSP Systems Engineering

Hubungi Elecguru011 tentang pekerjaan anda

Log masuk untuk membincangkan sebarang butiran melalui sembang.

Portfolio

Portfolio

25Hz Transmitter Coil

25Hz Transmitter Coil

25Hz Transmitter Coil

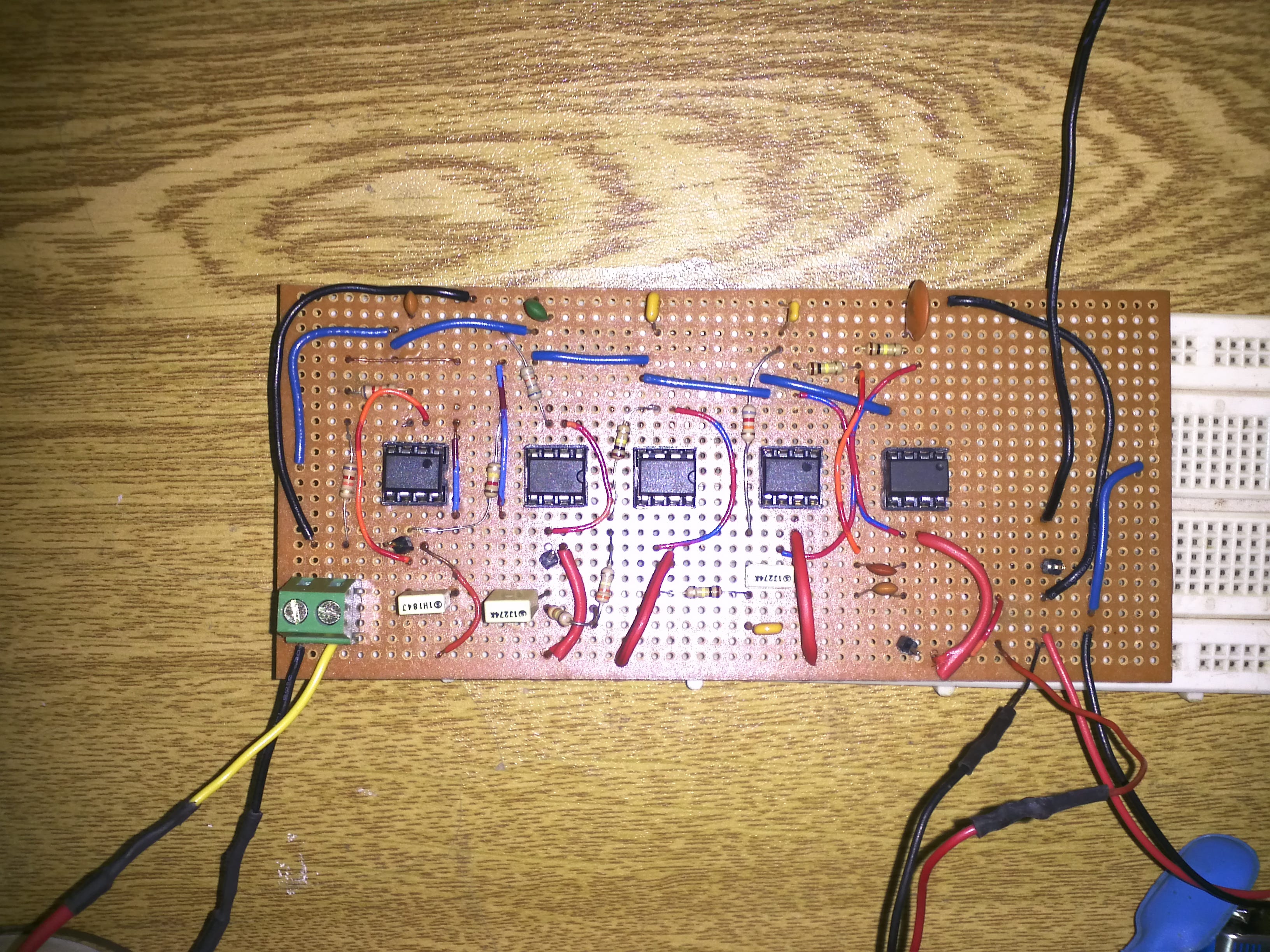

Sullen Key Filter

Sullen Key Filter

Sullen Key Filter

Sullen Key Filter

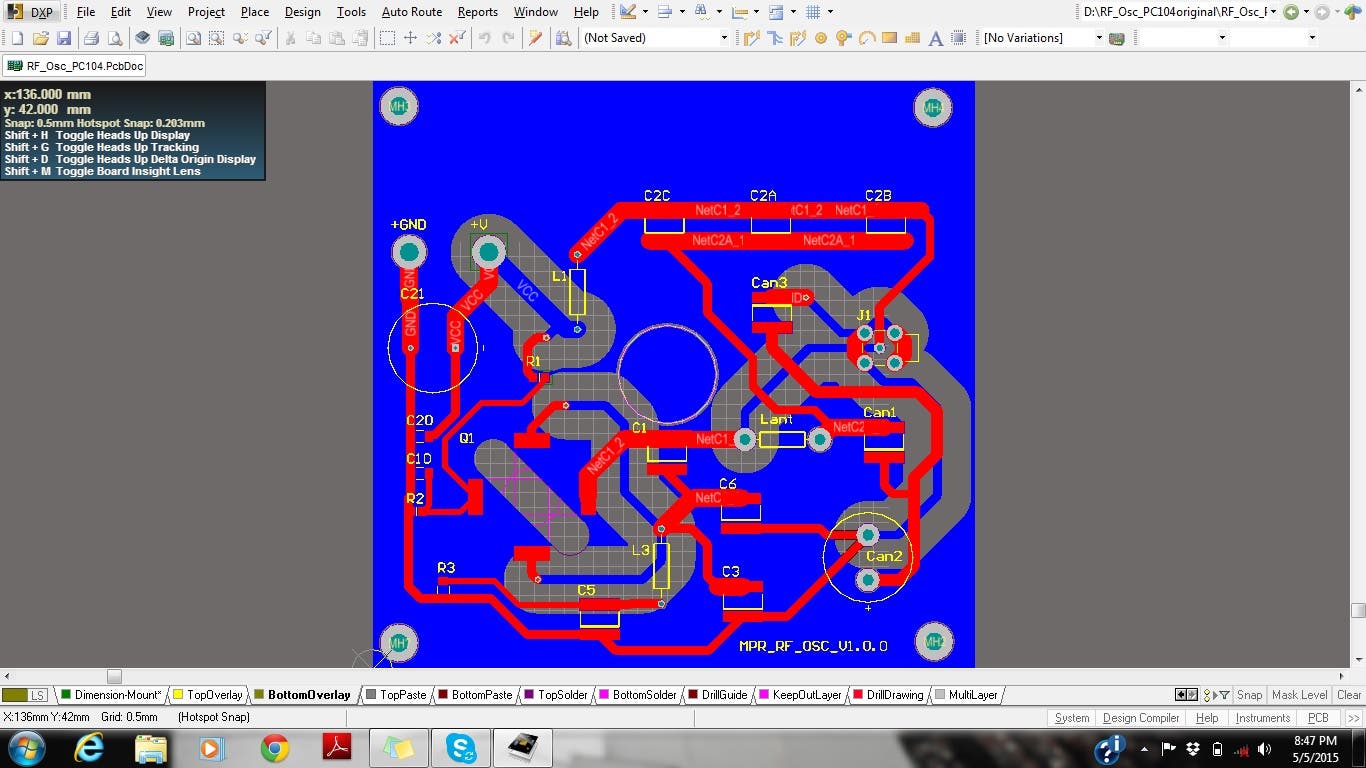

RF Oscillator

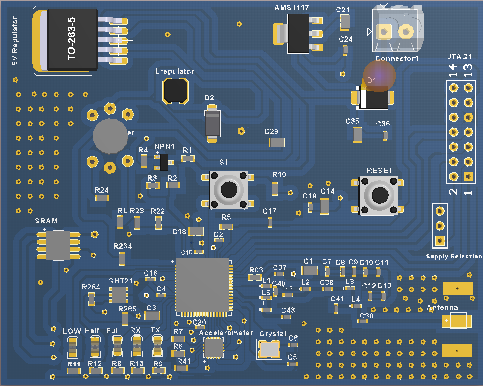

DASH-7 Wireless Board

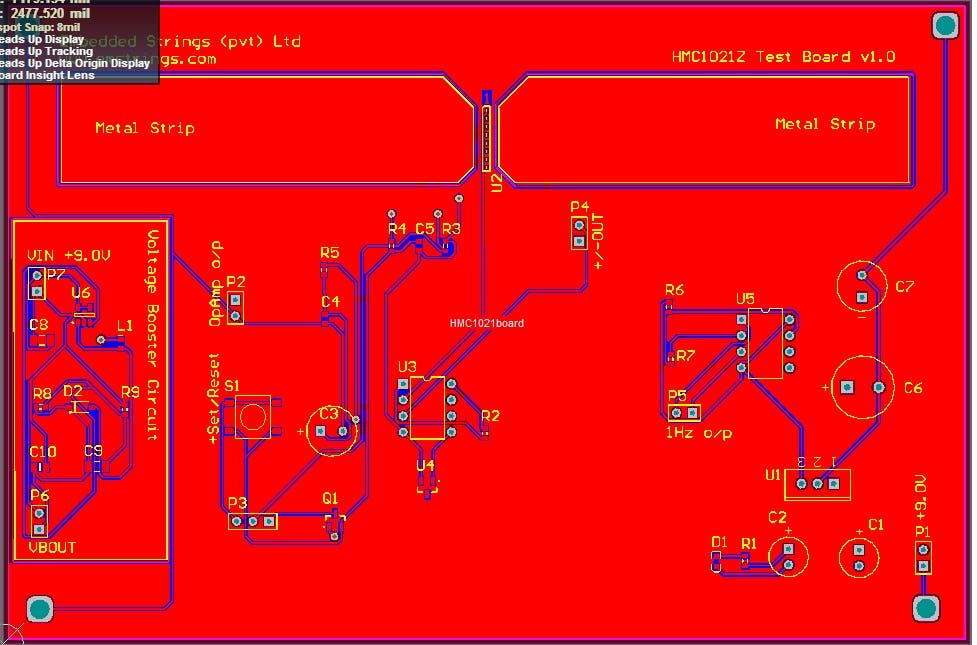

Altium PCB Design

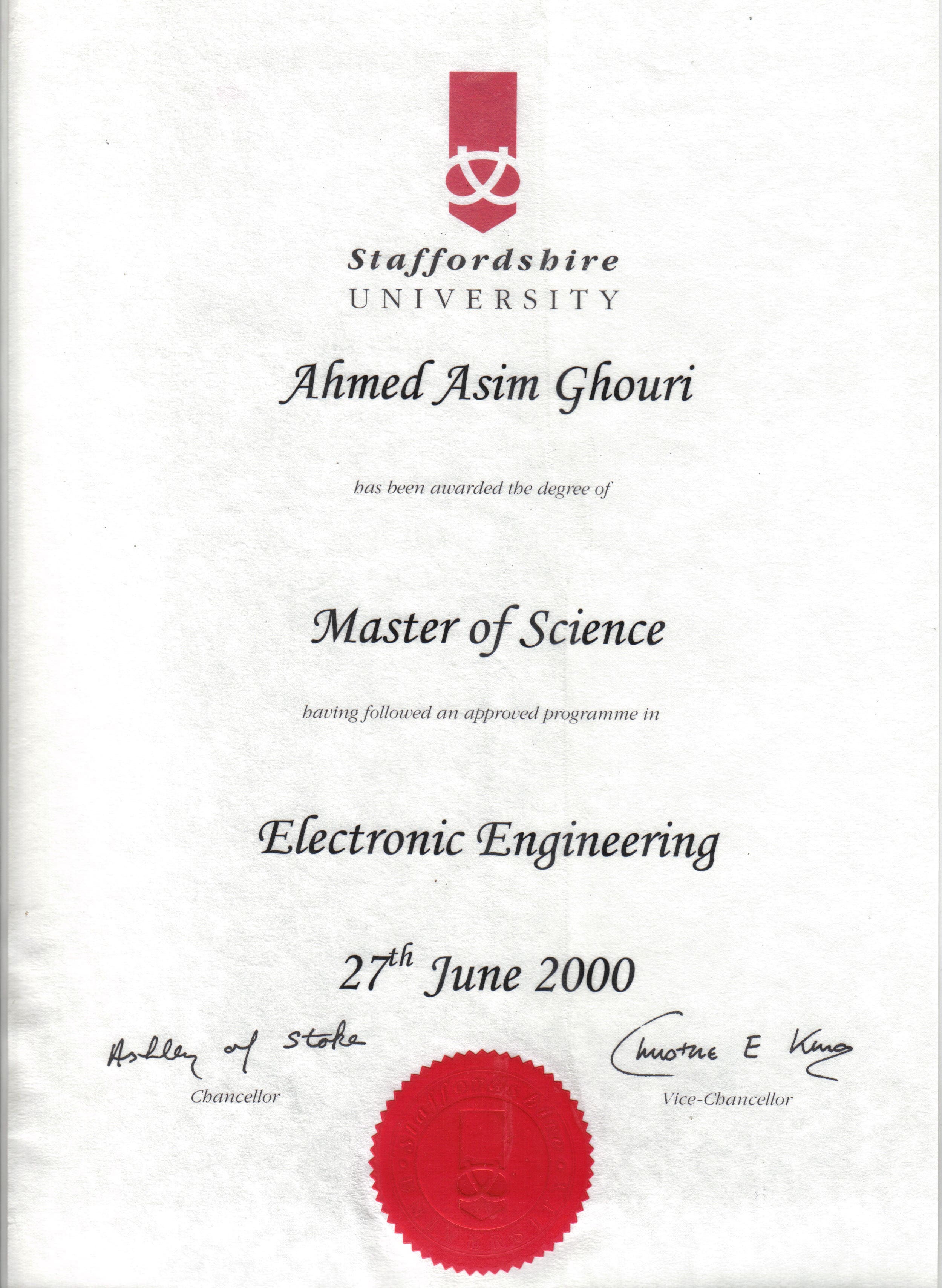

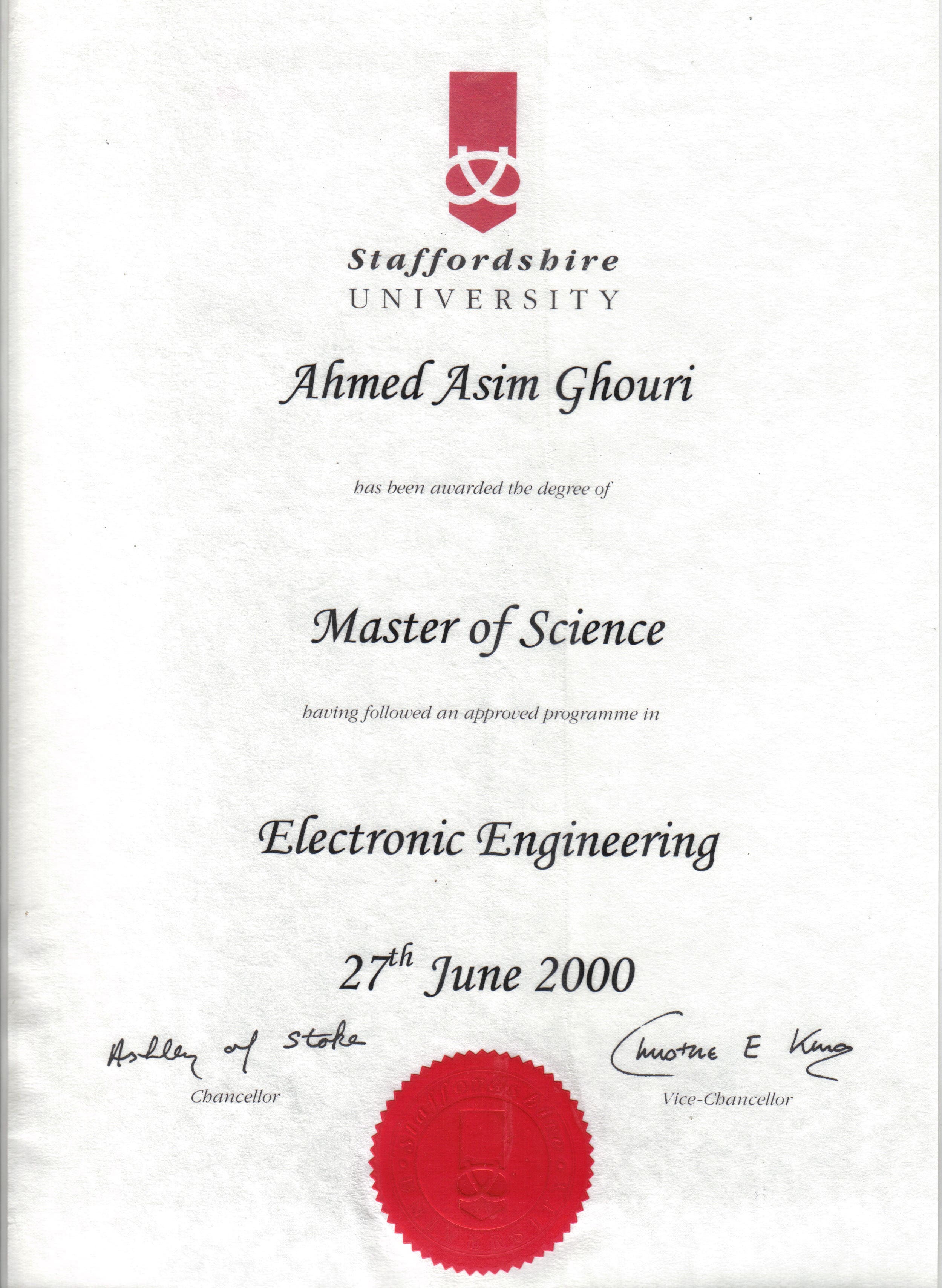

Masters of Electronics Engineering

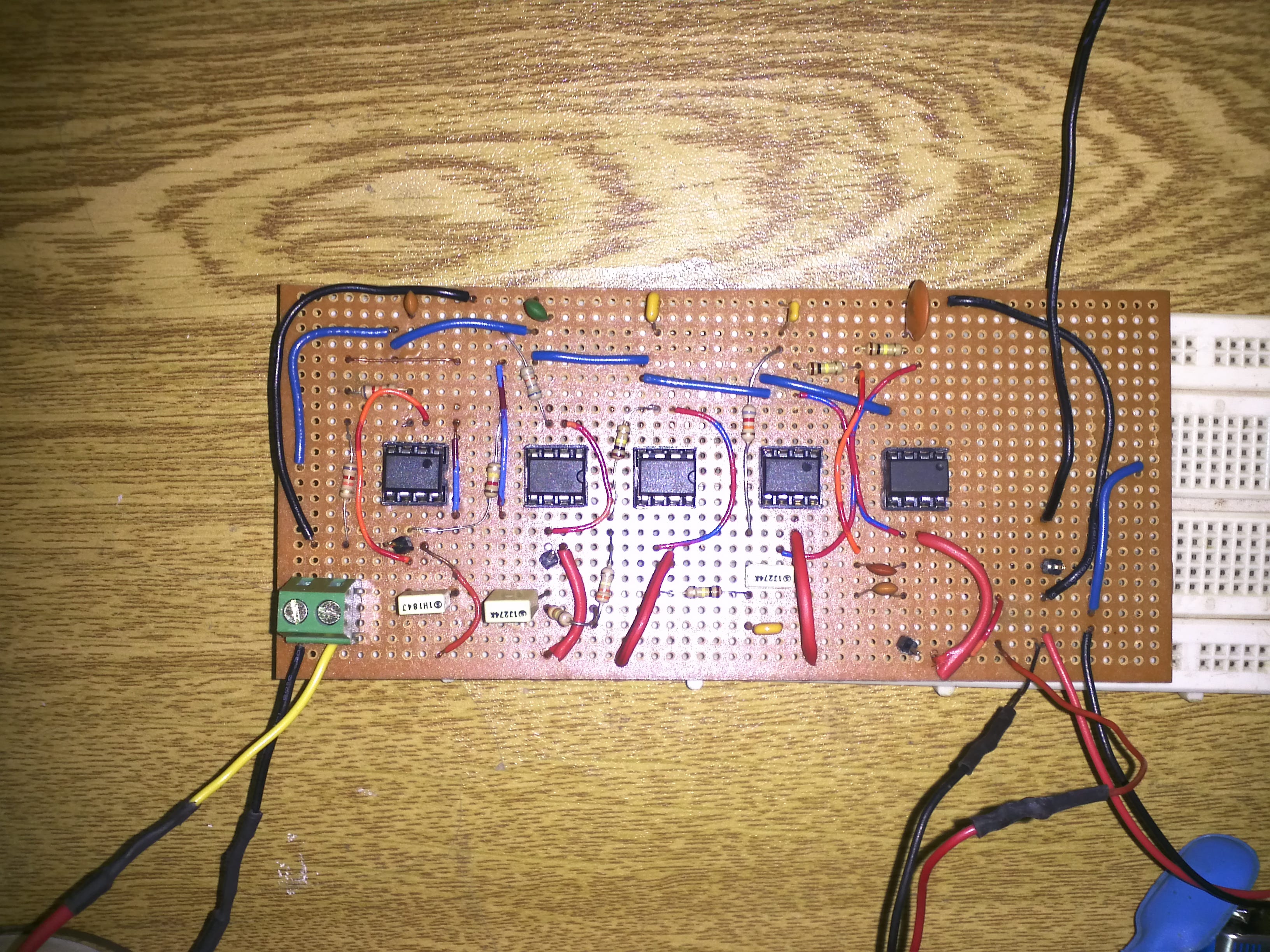

25Hz Transmitter Coil

25Hz Transmitter Coil

25Hz Transmitter Coil

Sullen Key Filter

Sullen Key Filter

Sullen Key Filter

Sullen Key Filter

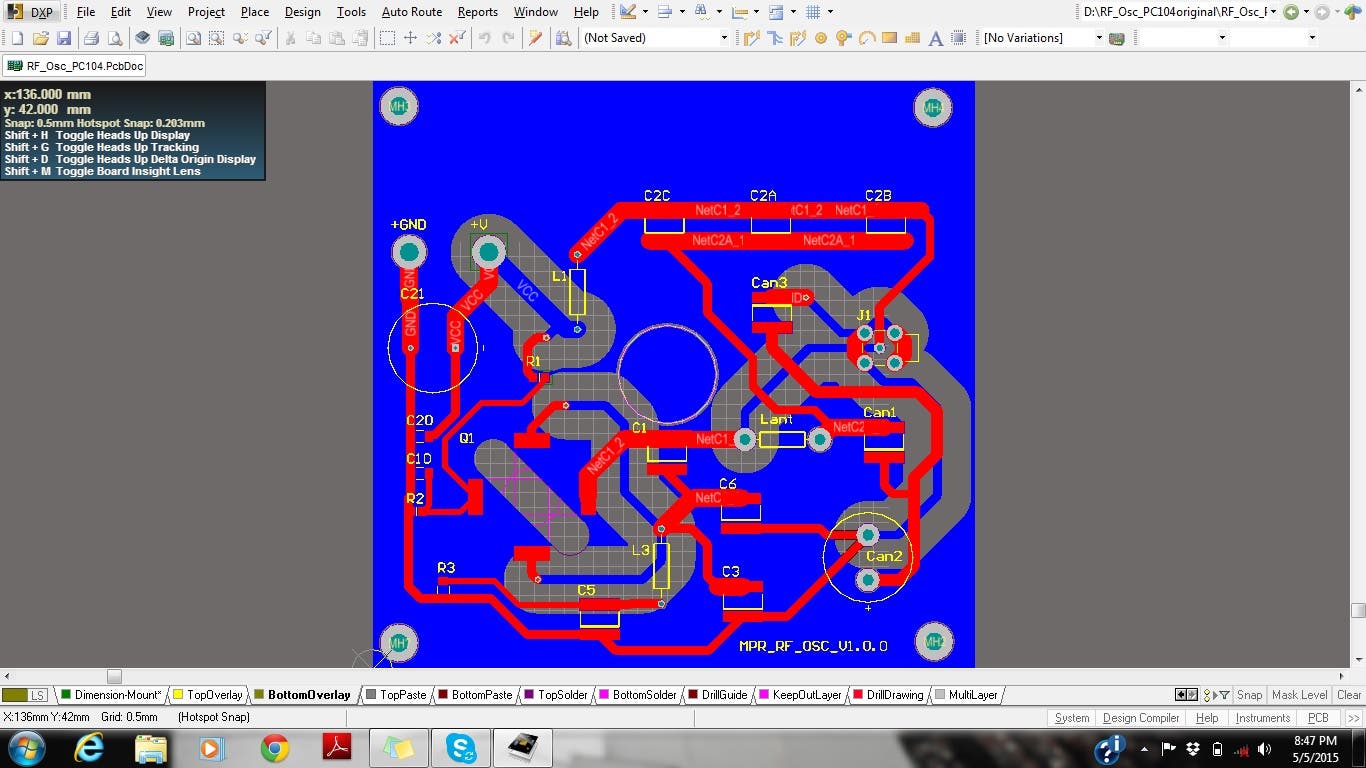

RF Oscillator

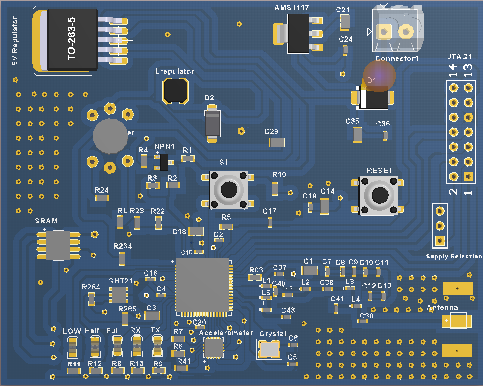

DASH-7 Wireless Board

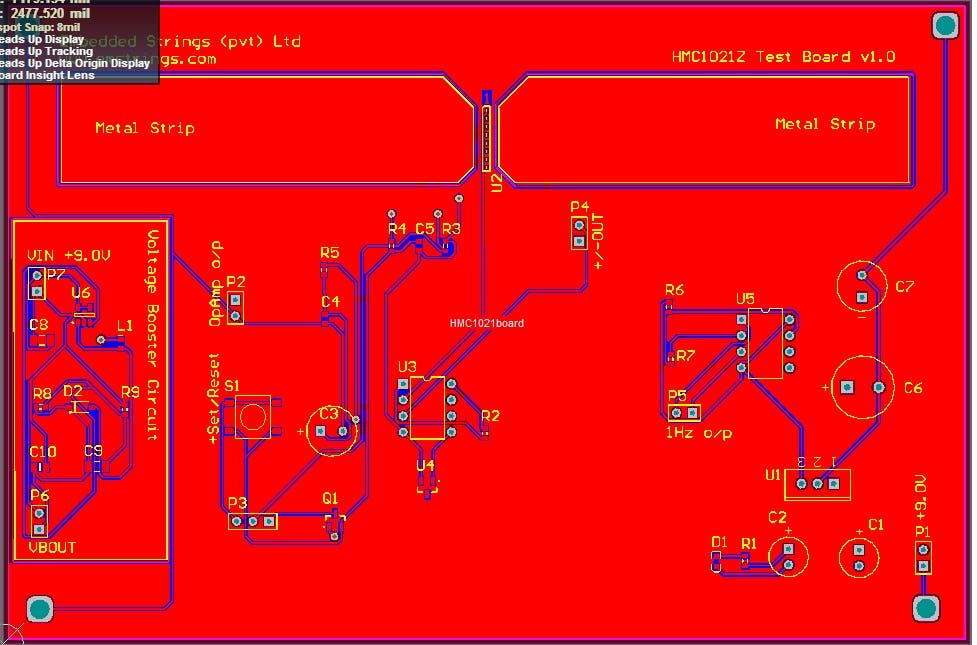

Altium PCB Design

Masters of Electronics Engineering

Ulasan

Perubahan disimpan

Menunjukkan 1 - 1 daripada 1 ulasan

$50.00 USD

Verilog / VHDL

FPGA

•

Pengalaman

Project Engineer

Jul 2015 - Hari ini

Embedded Systems design , FPGA and PIC Microcontroller based hardware design . Firmware and Software design and Systems analysis using Matlab.

Team Lead

Jan 2012 - Dis 2014 (2 tahun, 11 bulan)

I worked as Hardware Design group Team Lead , developed modules for wireless sensor network.

Digital and Analogue Design Engineer

Mei 2010 - Dis 2011 (1 tahun, 7 bulan)

FPGA Hardware Design of Satellite Communication system.

Pendidikan

M.Sc Telecommunication Engineering

(2 tahun)

MSc Electronics Engineering

(3 tahun)

Kelayakan

DSP Systems Engineering

University of California , Irvine

2012

Digital Signal Processing fundamentals, DFT,FFT , Digital Filter modelling and simulation using Matlab, FIR and IIR filter implementation on FPGA

Winner Best Design

Cypress Semiconductor

2004

Reconfigurable Logic using PSOC

Penerbitan

OTDR Implementation on FPGA

Embedded Strings (pvt)Ltd

Optical Time Domain Reflectrometery

In optical fiber communication, optical time domain reflectometery (OTDR) is a commonly used technique for characterization and fault location of optical fiber transmission systems. It involves measuring the fraction of a probe pulse that is scattered back (by Rayleigh scattering) from a silica fiber. Because of the very small levels of backscatter in single-mode fiber at long wavelengths, very sensitive optical detection is necessary to achieve adequate range performa

Audio Signal Processing

Ahmed A Ghouri

An audio signal frequency range is from 20Hz to 20Khz. In a music sample 20Khz bandwidth is required to encompass all harmonics. Although natural sounding speech only requires about 3.2Khz . Telecommunication systems typically operate with a sampling rate of about 8 kHz, allowing natural sounding speech, but greatly reduced music quality.

Here we are proposing a FPGA based audio signal filtering system which is reconfigurable and can be used as a Processing Engine to reduce background noise from a musi

Hubungi Elecguru011 tentang pekerjaan anda

Log masuk untuk membincangkan sebarang butiran melalui sembang.

Pengesahan

Pensijilan

Kemahiran Teratas

Layari Pekerja Bebas Serupa

Layari Pameran Serupa

Jemputan berjaya dihantar!

Terima kasih! Kami telah menghantar pautan melalui e-mel kepada anda untuk menuntut kredit percuma anda.

Sesuatu telah berlaku semasa menghantar e-mel anda. Sila cuba lagi.

Memuatkan pratonton

Kebenaran diberikan untuk Geolocation.

Sesi log masuk anda telah luput dan telah dilog keluar. Sila log masuk sekali lagi.