Anda kini mengikuti

Ralat mengikuti pengguna.

Pengguna ini tidak membenarkan pengguna untuk mengikuti mereka.

Anda telah mengikuti pengguna ini.

Pelan keahlian anda hanya membenarkan 0 mengikuti. Naik taraf di sini.

Berjaya menyahikut

Ralat tidak mengikuti pengguna.

Anda berjaya mengesyorkan

Ralat mengesyorkan pengguna.

Sesuatu telah berlaku. Sila segar semula halaman dan cuba lagi.

E-mel berjaya disahkan.

kathmandu,

nepal

Sekarang jam 10:11 PTG di sini

Menyertai Oktober 6, 2013

3 Cadangan

Krishna G.

@gaihrekrishna

1.4

1.4

50%

50%

kathmandu,

nepal

100%

Pekerjaan Disiapkan

100%

Mengikut Bajet

100%

Tepat Pada Masa

N/A

Kadar Upah Semula

FPGA Design + ML Acceleration Engineer

Hubungi Krishna G. tentang pekerjaan anda

Log masuk untuk membincangkan sebarang butiran melalui sembang.

Portfolio

Portfolio

Skunk Hash Algorithm Implementation on VCU/BCU 1525 FPGA

Cryptonight algorithm for Monero targeted VCU/BCU1525 FPGA

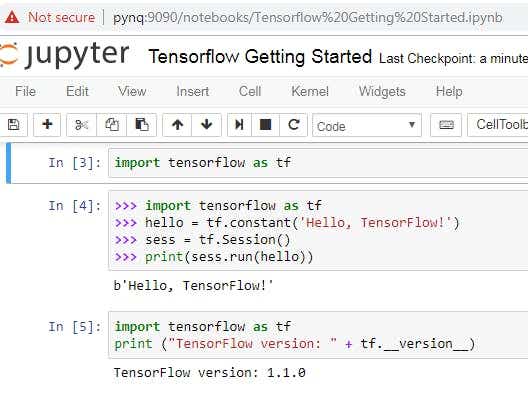

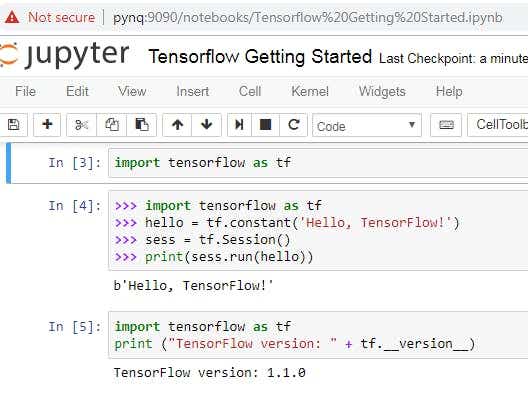

Tensorflow Installation on PYNQ FPGA

Tensorflow Installation on PYNQ FPGA

Crypto Implementation on FPGA

Video Processing with FPGA

Tensorflow Installation on PYNQ FPGA Session

Skunk Hash Algorithm Implementation on VCU/BCU 1525 FPGA

Cryptonight algorithm for Monero targeted VCU/BCU1525 FPGA

Tensorflow Installation on PYNQ FPGA

Tensorflow Installation on PYNQ FPGA

Crypto Implementation on FPGA

Video Processing with FPGA

Tensorflow Installation on PYNQ FPGA Session

Ulasan

Perubahan disimpan

Menunjukkan 1 - 1 daripada 1 ulasan

$50.00 USD

V

•

Pengalaman

FPGA Research Lead

Jun 2017 - Hari ini

Working on FPGA Development with VHDL, Verilog, HLS, MATLAB with Tools Xilinx VIVADO, HLS, SDK, SDSoC, SDAccel. I have expertise on Embedded System Design with Xilinx Zynq FPGA, Video Processing with Zynq, Machine Learning with FPGA, PYNQ Development, IP Development, Complete System Deployment on AWS, Nimbix and Plunify FPGA based Clouds.

FPGA Design Engineer

Jan 2013 - Mei 2017 (4 tahun, 4 bulan)

FPGA Design with VHDL/Verilog/Tcl and Xilinx Tools/Hardware

Pendidikan

M.Sc Engineering

(2 tahun)

Kelayakan

FPGA Trainer

Digitronix Nepal

2016

FPGA Training with Spartan and Zynq FPGA for Industrial and Academic Professionals.

Penerbitan

Face Detection and Recognition with PYNQ FPGA

FPGA World

The Face detection and recognition algorithm is implemented on the PYNQ FPGA. The VIVADO based overlay and Python methodology for face detection and recognition is followed on the PYNQ FPGA Board.

ARM Based Computing Technology for SD

IOE Graduate Conference

IOE Graduate Conference 2015

Hubungi Krishna G. tentang pekerjaan anda

Log masuk untuk membincangkan sebarang butiran melalui sembang.

Pengesahan

Kemahiran Teratas

Layari Pekerja Bebas Serupa

Layari Pameran Serupa

Jemputan berjaya dihantar!

Terima kasih! Kami telah menghantar pautan melalui e-mel kepada anda untuk menuntut kredit percuma anda.

Sesuatu telah berlaku semasa menghantar e-mel anda. Sila cuba lagi.

Memuatkan pratonton

Kebenaran diberikan untuk Geolocation.

Sesi log masuk anda telah luput dan telah dilog keluar. Sila log masuk sekali lagi.